在数字通信领域,信息传输方式主要分为串行与并行两大类。并行接口以其在特定历史时期和场景下的高速传输能力,曾广泛应用于计算机内部组件(如早期的IDE硬盘接口、打印机接口)及部分外设连接中。其核心原理在于利用多条物理通道同时传输多个数据位,从而实现单位时间内更高的理论带宽。

一、并行传输的基本原理

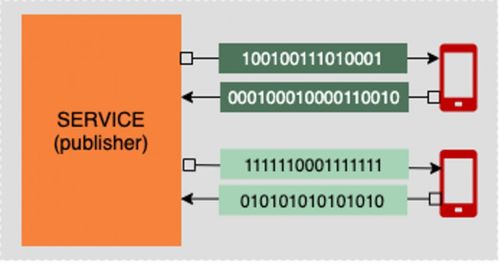

并行传输的本质是“空间换时间”。与串行接口逐位发送数据不同,一个典型的8位并行接口会使用8条独立的数据线(即一个“字节宽”的总线),加上必要的控制线(如选通、应答、忙信号)和地线。当需要发送一个字节(8位)的数据时,这8位数据会分别被放置在这8条数据线上,在一个时钟周期或选通信号的触发下,同时从发送端传送到接收端。例如,传输ASCII字符‘A’(二进制01000001),那么D0线为高电平(1),D1线为低电平(0),以此类推,所有线路状态同时确立并被读取。

二、关键技术与工作流程

- 数据线宽与带宽:数据线的数量(如8位、16位、32位)直接决定了每次能并行传输的数据量。这是其早期速度优势的基础。

- 握手协议(Handshaking):这是确保数据可靠传输的核心。通常采用“选通-应答”机制。发送端将数据置于数据线并稳定后,发出一个“选通”(STROBE)信号;接收端收到此信号后读取数据,完成后回送一个“应答”(ACK)信号;发送端收到ACK后,方可进行下一次传输。此流程解决了双方速度不匹配的问题。

- 时钟同步:有些并行接口(如CPCI)使用公共时钟信号同步所有线路的数据收发,称为同步并行传输。而无独立时钟,依靠选通信号触发的,则属于异步并行传输(如标准并口)。

三、优势与局限性分析

优势在于原理直观,在短距离、低频率下,能实现较高的聚合带宽。在处理器与缓存、早期内存与北桥芯片等板内高速互连中表现突出。

其局限性随着频率提升而日益凸显,这也导致了其在长距离通信和高速领域被串行接口取代:

- 信号偏移(Skew):这是并行传输最致命的弱点。由于不同数据线在PCB走线长度、电气特性上的微小差异,导致同时发出的信号无法完全同时到达接收端。频率越高,位周期越短,微小的延迟差异就足以导致接收端在采样时刻读取到错误的数据。

- 串扰(Crosstalk):密集排列的并行导线在高频下会产生严重的电磁干扰,彼此影响信号完整性。

- 接口庞大与成本:多条数据线、控制线导致接口 connector 体积大、线缆粗重且成本高,不利于设备小型化。

- 同步困难:如前所述,在高速下保证所有线路严格同步极其困难。

四、典型应用与演进

经典应用包括:

- IEEE 1284标准并行端口(俗称“打印口”):曾用于连接打印机、扫描仪和外置驱动器。

- PATA(IDE)硬盘接口:使用40或80线缆并行传输数据。

- 早期内存接口:如SDRAM采用的并行总线。

其演进路径清晰地反映了技术趋势:为了克服信号偏移,PATA从40线增至80线(新增40根地线用于隔离干扰);但根本解决方案是转向高速串行接口。现代技术如PCI Express、SATA、USB等,虽然名义上是“串行”,但通过采用差分信号、嵌入时钟、数据包化、以及多通道并行(多个串行通道捆绑,在物理层并行,在逻辑层仍串行处理) 等技术,在物理层简化了同步难题,同时在逻辑上实现了比传统并行总线高得多的实际带宽。

###

总而言之,并行接口信息传输原理代表了通过增加物理通道来提升带宽的直接思路。它的兴衰史是电子工程中权衡速度、距离、成本和信号完整性的生动一课。尽管在高速长距领域已让位于更先进的串行方案,但其设计思想——尤其是多通道并发处理数据的概念——依然以新的形式(如多车道PCIe通道、DDR内存的多bank操作)深刻影响着现代计算机体系结构。理解并行传输,是理解计算机内部高速数据流协同工作的基础。